Integracija procesorskega jedra z vmesnikom NFC

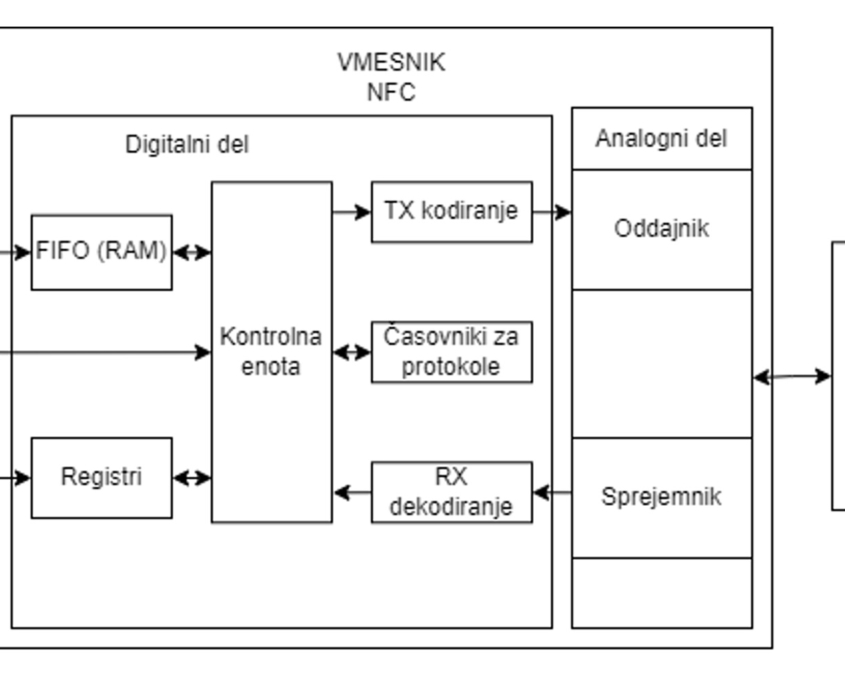

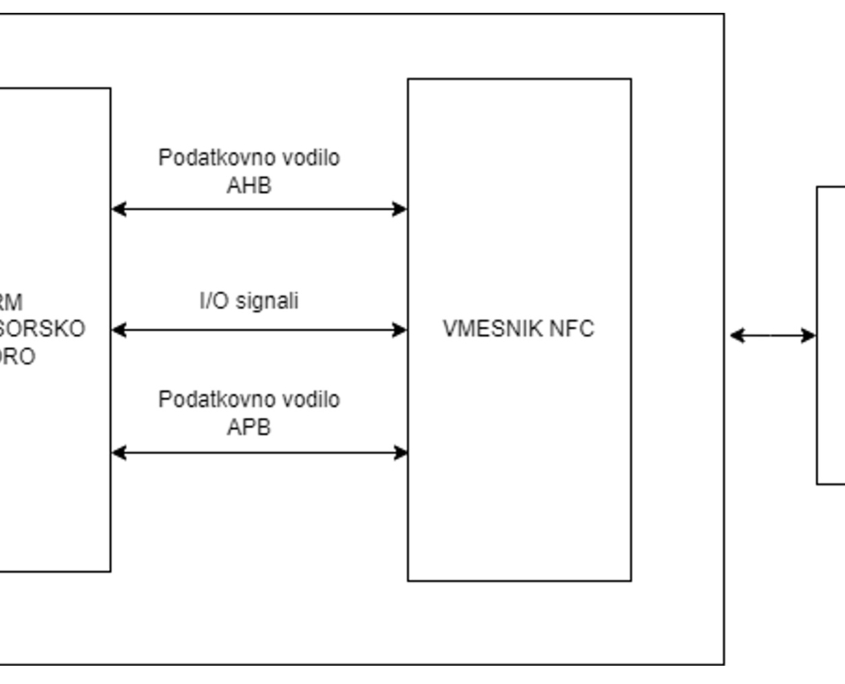

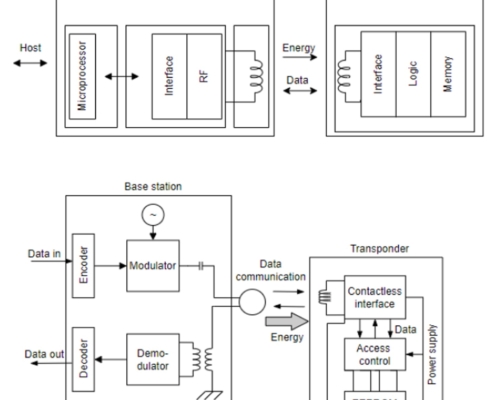

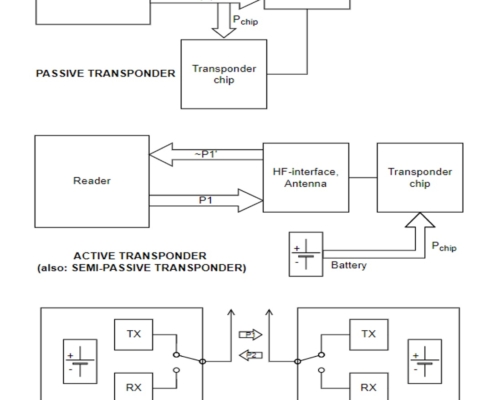

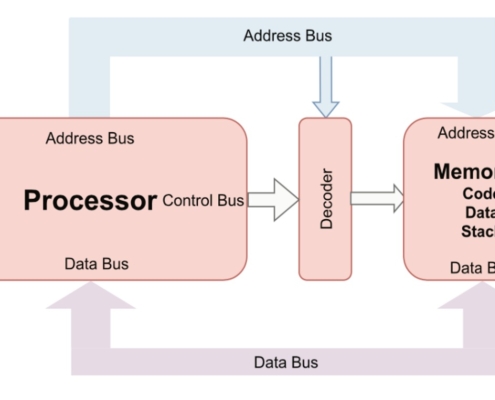

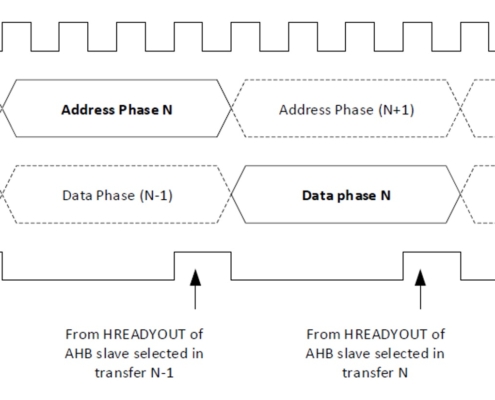

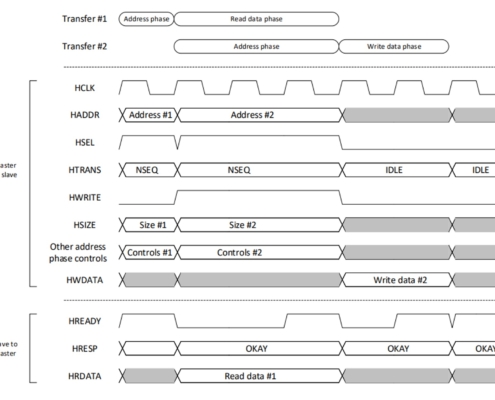

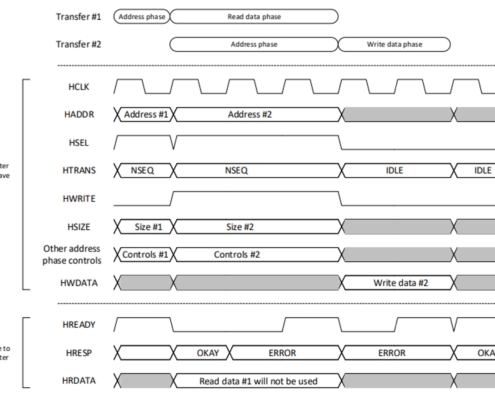

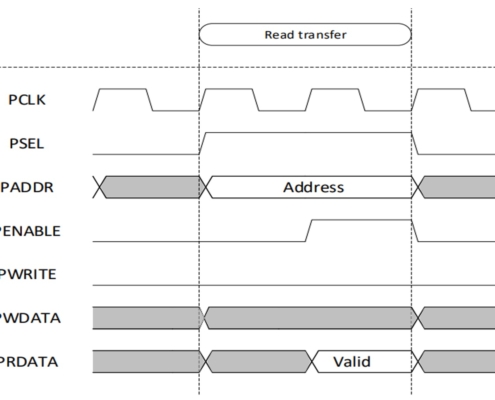

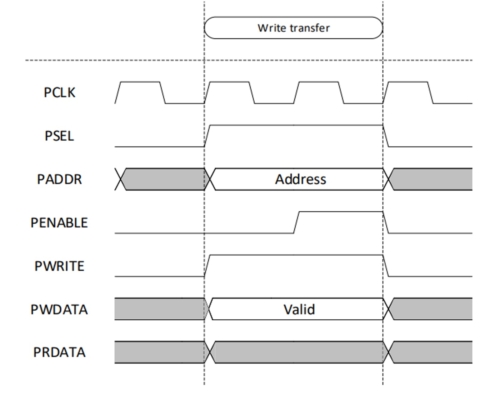

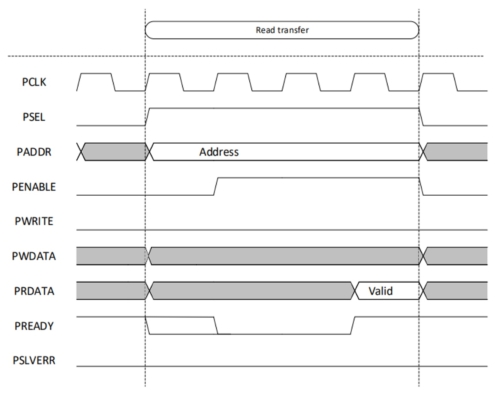

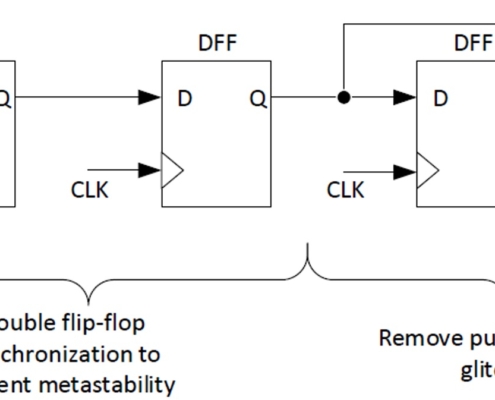

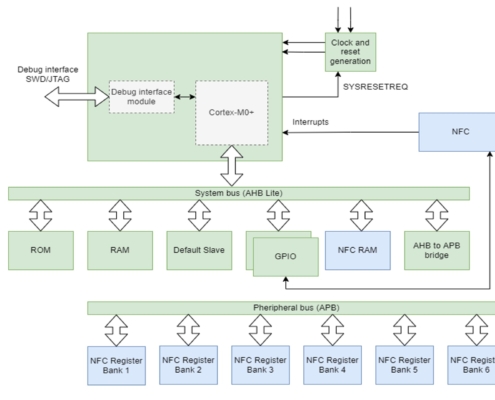

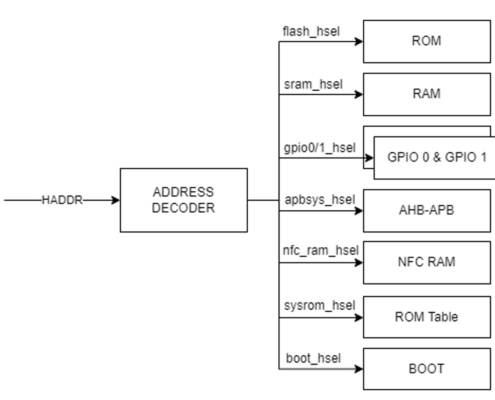

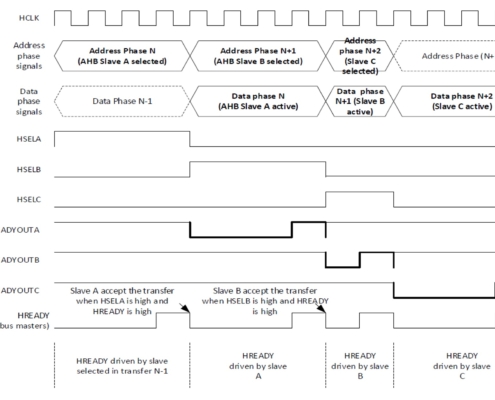

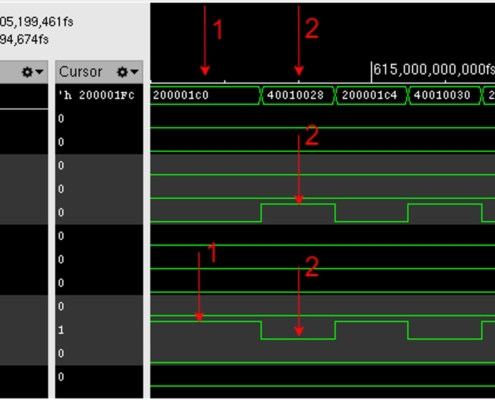

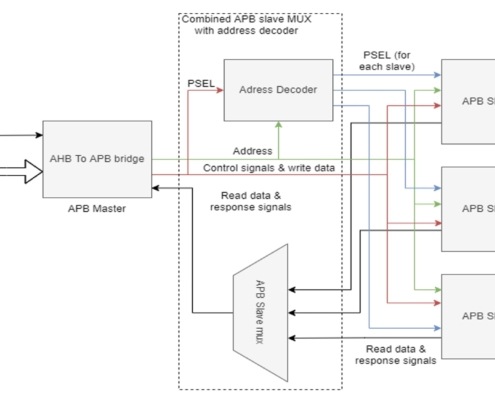

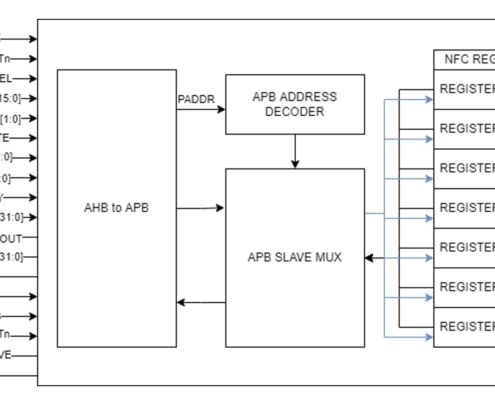

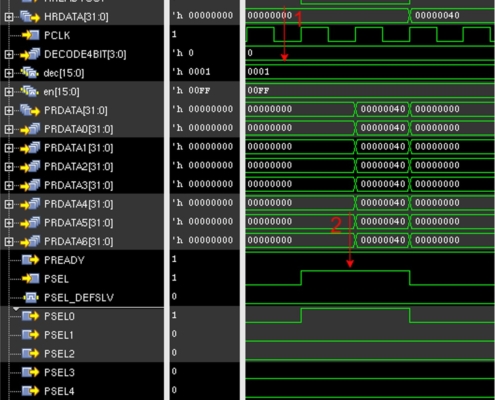

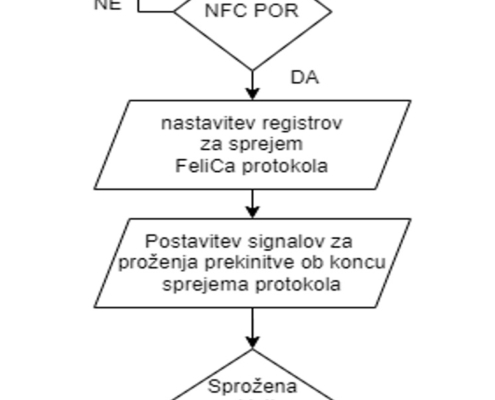

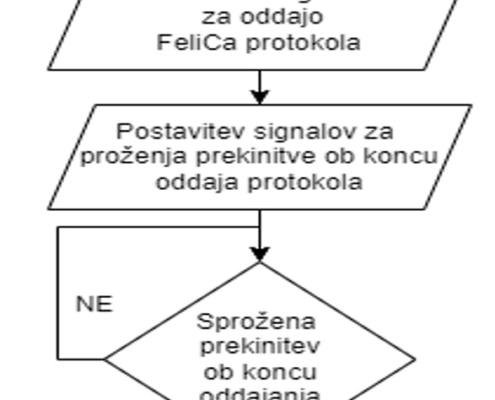

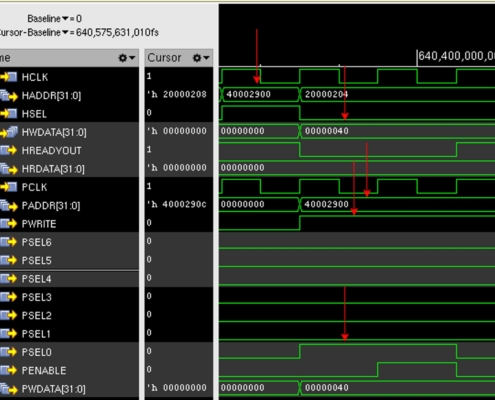

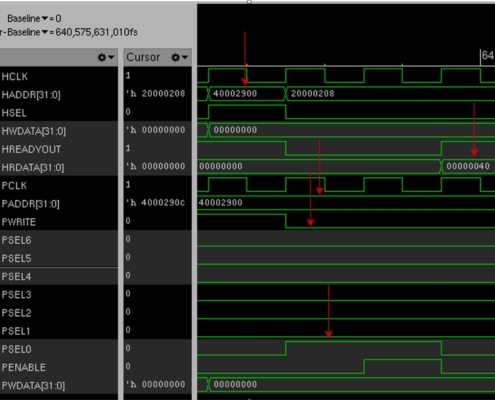

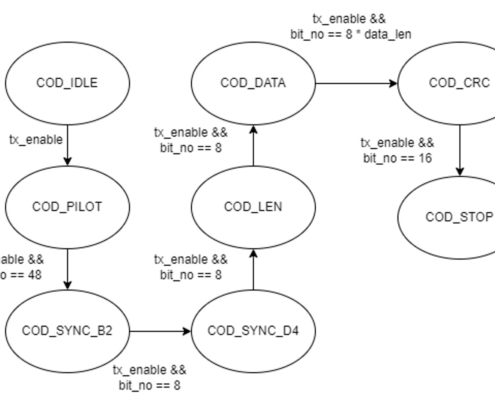

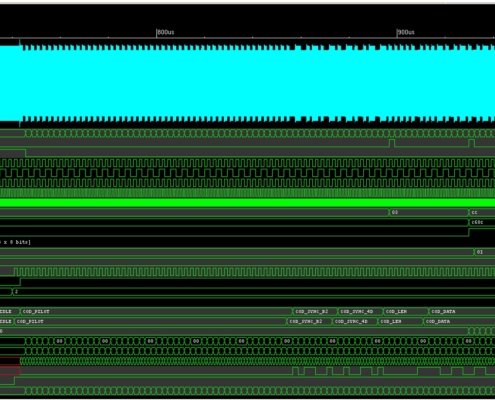

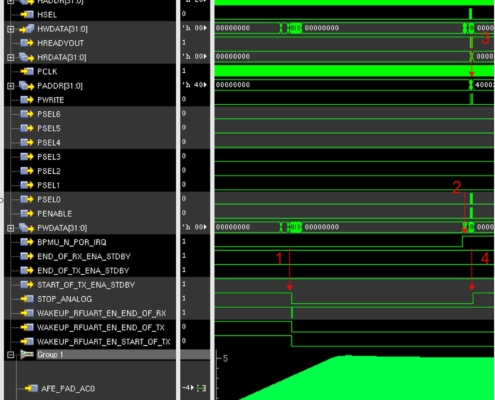

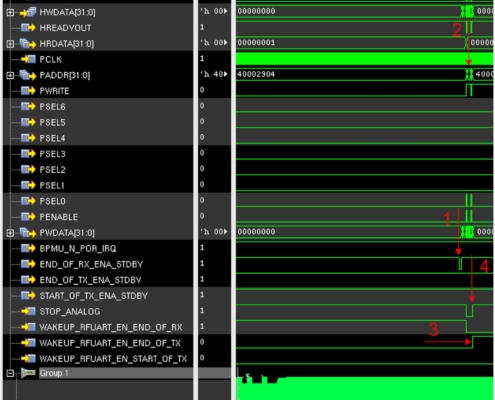

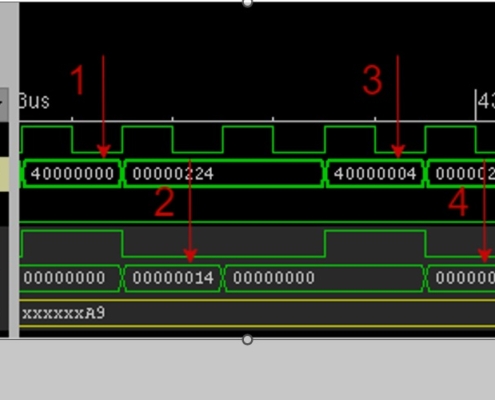

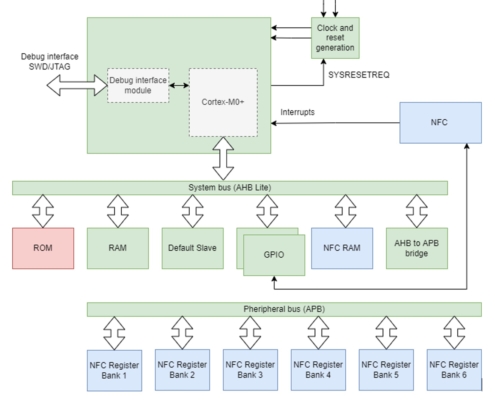

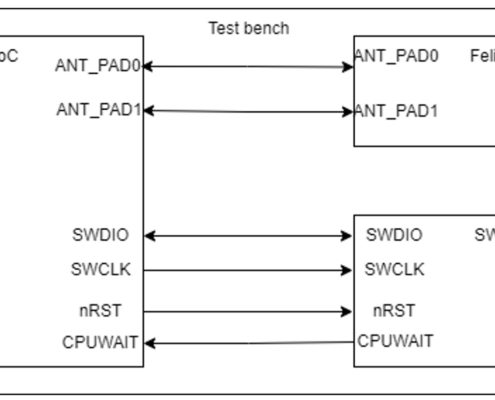

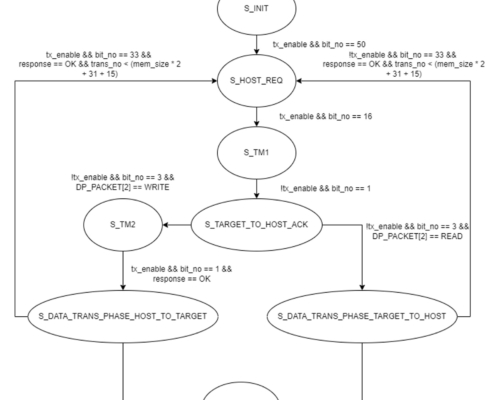

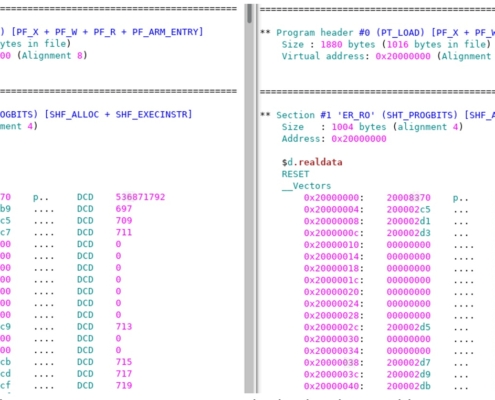

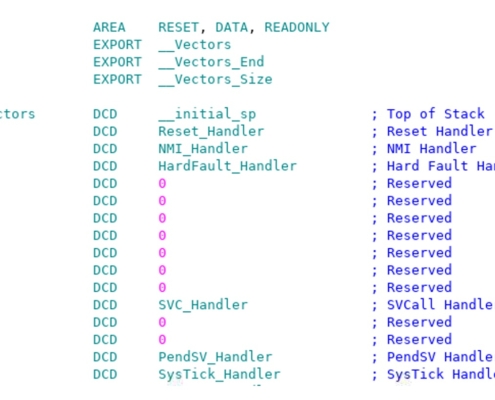

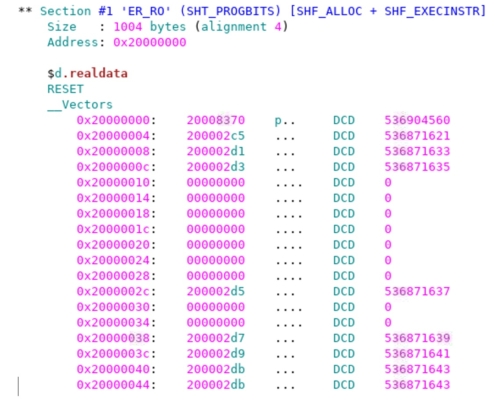

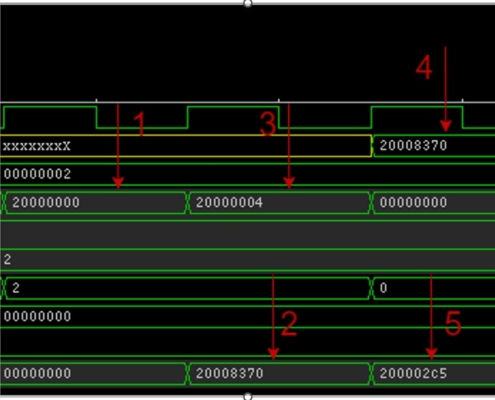

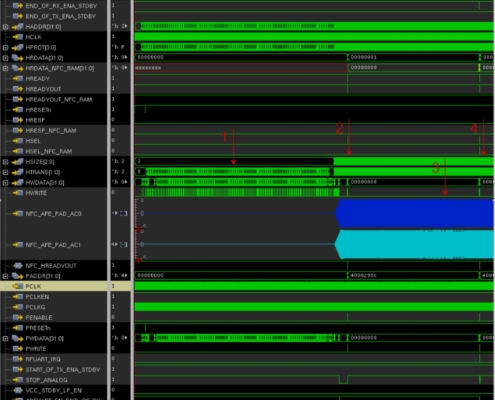

Vmesnik NFC je sestavljen iz digitalnega in analognega dela. V analognem delu se nahajajo bloki, ki skrbijo za pravilen sprejem in oddajo različnih tipov modulacij. Ta del vsebuje različne modulatorje, demodulatorje, priključke za napajanje in antenske priključke, preko katerih se oddaja ali sprejema signal, ki ga želimo modulirati ali demodulirati. V digitalnem delu pa se nahajajo kontrola podatkov za kodiranje, dekodiranje, registri, preko katerih nastavimo želene modulacije, stanja vmesnika NFC, ne glede na to, ali je NFC napajan preko baterije ali samo preko polja, ki ga sprejme vmesnik NFC. Digitalni del skrbi tudi za različne funkcije, in različne prekinitve, ki skrbijo za zbuditev procesorja iz spanja in razne kontrolne bloke za analogni del. V digitalnem delu se nahajata tudi podatkovni vodili AHB in APB. Podatkovno vodilo AHB skrbi za komunikacijo z notranjim pomnilnikom vmesnika NFC. Slednji ima svoj pomnilnik, v katerega po sprejemu vpisuje podatke, v primeru oddajanja pa iz pomnilnika bere podatke, ki jih mora oddati preko analognega dela, kjer se potem modulirajo skladno s protokolom. Podatkovno vodilo APB skrbi za dostop do posameznih registrov vmesnika NFC, kjer se nastavljajo protokoli in prekinitve. Za priključitev vmesnika NFC v procesorsko jedro smo morali izdelati novo arhitekturo vodila AHB, kjer smo definirali posamezne lokacije komponent sistema. Na vodila smo priključili ROM, v katerega v začetnih fazah razvoja shranjujemo programsko kodo, RAM, ki uporabljamo za shranjevanje podatkov, privzeti suženj, dva vmesnika GPIO, RAM vmesnika NFC in AHB-APB most. Na vmesnik GPIO smo priklopili tudi signale za krmiljenje NFC vmesnika.